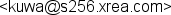

H8とFPGAが接続されたボードとして、 ストロベリーリナックスの SPARTAN-COMPLETE を使います。 (数年前に買ったものなのですが、長いこと箪笥の肥やしになってしまっていました・・・。)

H8からはメモリマップされたI/Fレジスタを介して、使えるようにします。

| アドレス | レジスタ名 | 機能 |

|---|---|---|

| 0 | DATA0 | データ0 |

| 1 | DATA1 | データ1 |

| 2 | CTRL | データ0とデータ1に対する演算指定(0:加算、1:減算) |

| 3 | STATUS | 演算結果 |

H8ソフトから見て、

バスコントローラ設定としては、 エリア4について、

BSC.CSCR.BIT.CS4E = 1;あるいは、

*((unsigned char *)0xfee01f) = 0x1f;

BSC.ABWCR.BIT.ABW4 = 1;あるいは、

*((unsigned char *)0xfee020) = 0xff;

BSC.ASTCR.BIT.AST4 = 1;あるいは、

*((unsigned char *)0xfee021) = 0xff;

BSC.WCR.BIT.W4 = 0;あるいは、

*((unsigned char *)0xfee022) = 0xfc;

なお、Verilogソースは以下の通り:

module top(CLK, nRST, nCS, nWE, nOE, ADDR, DATA, nAS);

input CLK;

input nRST;

input nCS;

input nWE;

input nOE;

input [2:0] ADDR;

inout [7:0] DATA;

input nAS;

// Registers

reg [7:0] REG_DATA0;

reg [7:0] REG_DATA1;

reg [7:0] REG_CTRL;

reg [7:0] REG_STATUS;

// Chip Select Signals

wire CS_REG_DATA0;

wire CS_REG_DATA1;

wire CS_REG_CTRL;

wire CS_REG_STATUS;

// Address Decoder

assign CS_REG_DATA0 = ~nCS & ~nAS & (ADDR == 3'b000);

assign CS_REG_DATA1 = ~nCS & ~nAS & (ADDR == 3'b001);

assign CS_REG_CTRL = ~nCS & ~nAS & (ADDR == 3'b010);

assign CS_REG_STATUS = ~nCS & ~nAS & (ADDR == 3'b011);

assign CS_REG_UNASSIGN = ~nCS & ~nAS & (ADDR[2] == 1'b1);

// Data 0 Register

always @(posedge CLK or negedge nRST)

if (nRST == 0)

REG_DATA0 <= 8'b0;

else if (CS_REG_DATA0 & ~nWE)

REG_DATA0 <= DATA;

// Data 1 Register

always @(posedge CLK or negedge nRST)

if (nRST == 0)

REG_DATA1 <= 8'b0;

else if (CS_REG_DATA1 & ~nWE)

REG_DATA1 <= DATA;

// Control Register

always @(posedge CLK or negedge nRST)

if (nRST == 0)

REG_CTRL <= 8'b0;

else if (CS_REG_CTRL & ~nWE)

REG_CTRL <= DATA;

// Status Register

always @(posedge CLK or negedge nRST)

if (nRST == 0)

REG_STATUS <= 8'b0;

else

if (REG_CTRL == 8'b0)

REG_STATUS <= REG_DATA0 + REG_DATA1;

else

REG_STATUS <= REG_DATA0 - REG_DATA1;

// Data Bus Output

assign DATA =

(CS_REG_DATA0 & ~nOE) ? REG_DATA0 :

(CS_REG_DATA1 & ~nOE) ? REG_DATA1 :

(CS_REG_CTRL & ~nOE) ? REG_CTRL :

(CS_REG_STATUS & ~nOE) ? REG_STATUS :

(CS_REG_UNASSIGN & ~nOE) ? 8'b0 :

8'bz;

endmodule // top

H8とI/Fする部分の設計についてちょっとだけ述べます。

※

すみません。まじめに設計&検証していません。(;´Д`)

プロはステートマシンを組んだりするのでしょうが、やってません。

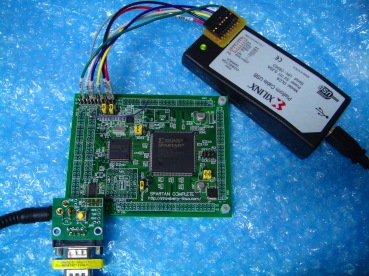

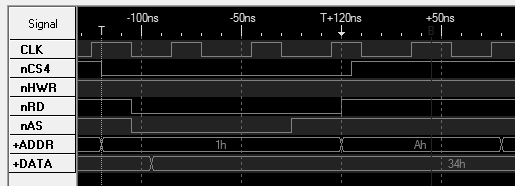

タイミングについては、

マニュアルの

「図21.13 基本バスタイミング/2ステートアクセス」

「図21.14 基本バスタイミング/3ステートアクセス」

「表21.6 バスタイミング」

とつき合わせて検証する必要があります。

作った後ですが、一応、ロジアナで実波形を見てみました。

# NET "CLK" LOC = "P185" ; NET "ADDR<0>" LOC = "P181" ; NET "ADDR<1>" LOC = "P180" ; NET "ADDR<2>" LOC = "P179" ; NET "DATA<0>" LOC = "P195" ; NET "DATA<1>" LOC = "P194" ; NET "DATA<2>" LOC = "P193" ; NET "DATA<3>" LOC = "P192" ; NET "DATA<4>" LOC = "P191" ; NET "DATA<5>" LOC = "P189" ; NET "DATA<6>" LOC = "P188" ; NET "DATA<7>" LOC = "P187" ; NET "nWE" LOC = "P147" ; NET "nOE" LOC = "P150" ; NET "nCS" LOC = "P149" ; NET "nRST" LOC = "P138" | PULLUP ; NET "nAS" LOC = "P139" ;

同じ内容を表にすると以下の通りです:

| H8/3069の信号名 | FPGAの信号名 | SPARTAN-COMPLETEの基板I/O端子番号 |

|---|---|---|

| A0 | P181 | CH4-26 |

| A1 | P180 | CH4-25 |

| A2 | P179 | CH4-24 |

| D8 | P195 | CH4-40 |

| D9 | P194 | CH4-39 |

| D10 | P193 | CH4-38 |

| D11 | P192 | CH4-37 |

| D12 | P191 | CH4-36 |

| D13 | P189 | CH4-35 |

| D14 | P188 | CH4-34 |

| D15 | P187 | CH4-33 |

| /HWR | P147 | CH3-40 / CH7-7 |

| /RD | P150 | CH3-43 / CH7-6 |

| /CS4 | P149 | CH3-42 |

| /AS ※ | P139 | CH3-35 / CH7-5 |

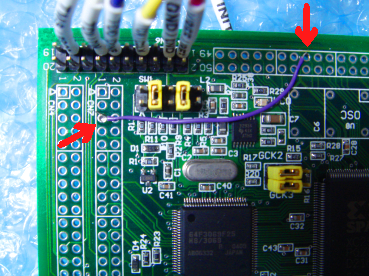

※

H8の/AS(アドレスストローブ)がFPGAにつながっていないので、つなぎます。

具体的には、

私は以下の写真のように

SPARTAN-COMPLETEボードのCH7-5番(H8の/AS)とCH3-35番(FPGAのP139)を

線でつなぎました。(半田付け)

FPGAに書き込むtop.bitができるとこまでやります。

ただし、SPARTAN-COPLETEは25MHzクロックを使っているので、 以下の変更が必要です。 monix/sys.hの

# define CPU_HZ 20 /* MHz */を

# define CPU_HZ 25 /* MHz */に変えます。

これでビルドしたものを使います。

ビルドしたmonix.motをH8の内蔵ROMに書きます。

※ SPARTAN-COMPLETEには、Ether、DRAM等の周辺がないので 無効にした方がいいですが、 今回はそのままでアクセスしないようにします。

MONIX Ver.0.1 (Jan 27 2007, 17:47:37) BootMode: 0x00 1:db 0x800000 128 →FPGAのエリアをダンプしてみる。(そもそもバスコントローラを設定してないので見えない。) 800000 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800010 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800020 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800030 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800040 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800050 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800060 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 800070 ffff ffff ffff ffff - ffff ffff ffff ffff ................

top.bitをISE(の書き込みツールIMPACT)を使ってFPGAに書き込みます。※

※ 私はコンフィグROMを搭載してないSPARTAN-COMPLETEを買ったので、 電源を入れ直すたびに書き込みをする必要があります。

ロジックを書けたら、まずはH8のバスコントローラを設定して、 FPGAにアクセスできるようにします。

準備ができたので、動くか試してみます。1:db 0xfee010 64 fee010 ffc5 09fe 0000 37ff - 0000 fefc 7800 ff0f ......7.....x... fee020 ffff ffff c6ff 3898 - 9723 3098 7f00 0000 ......8..#0..... fee030 ffff ffff ffff ffff - ff00 ffff 00ff 00f0 ................ fee040 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 1:fb 0xfee01f 1 0x1f →/CS4をイネーブル。 1:fb 0xfee020 1 0xff →エリア4を8bit幅アクセスに。(デフォルトで8bit幅アクセスなので、これはやらなくてよい) 1:fb 0xfee021 1 0xff →エリア4を3ステートアクセスに。(デフォルトで3ステートアクセスなので、これもやらなくてよい) 1:fb 0xfee022 1 0xfc →エリア4アクセス時プログラムウェイトを挿入しない。 1: 1:db 0xfee010 64 →設定できたことを確認。 fee010 ffc5 09fe 0000 37ff - 0000 fefc 7800 ff1f ......7.....x... fee020 ffff fcff c6ff 3898 - 9723 3098 7f00 0000 ......8..#0..... fee030 ffff ffff ffff ffff - ff00 ffff 00ff 00f0 ................ fee040 ffff ffff ffff ffff - ffff ffff ffff ffff ................ 1: 1: 1:db 0x800000 128 →エリア4(FPGA)の先頭128バイトを表示。(さっきはffffだったのが、0000になった) 800000 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800010 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800020 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800030 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800040 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800050 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800060 0000 0000 0000 0000 - 0000 0000 0000 0000 ................ 800070 0000 0000 0000 0000 - 0000 0000 0000 0000 ................

1:fb 0x800000 1 0x32 →DATA0レジスタに0x32をライト。 1:fb 0x800001 1 0x10 →DATA1レジスタに0x10をライト。 1:db 0x800000 128 →ダンプ。(CTRLレジスタが0 (すなわち「加算」)なので、STATUSレジスタがDATA0+DATA1=0x42になった!) 800000 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800010 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800020 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800030 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800040 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800050 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800060 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 800070 3210 0042 0000 0000 - 3210 0042 0000 0000 2..B....2..B.... 1:fb 0x800002 1 0x01 →CTRLレジスタに1(すなわち「減算」)をライト。 1:db 0x800000 128 →ダンプ。(CTRLレジスタが1 (すなわち「減算」)なので、STATUSレジスタがDATA0-DATA1=0x22になった!) 800000 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800010 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800020 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800030 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800040 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800050 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800060 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 800070 3210 0122 0000 0000 - 3210 0122 0000 0000 2.."....2..".... 1: